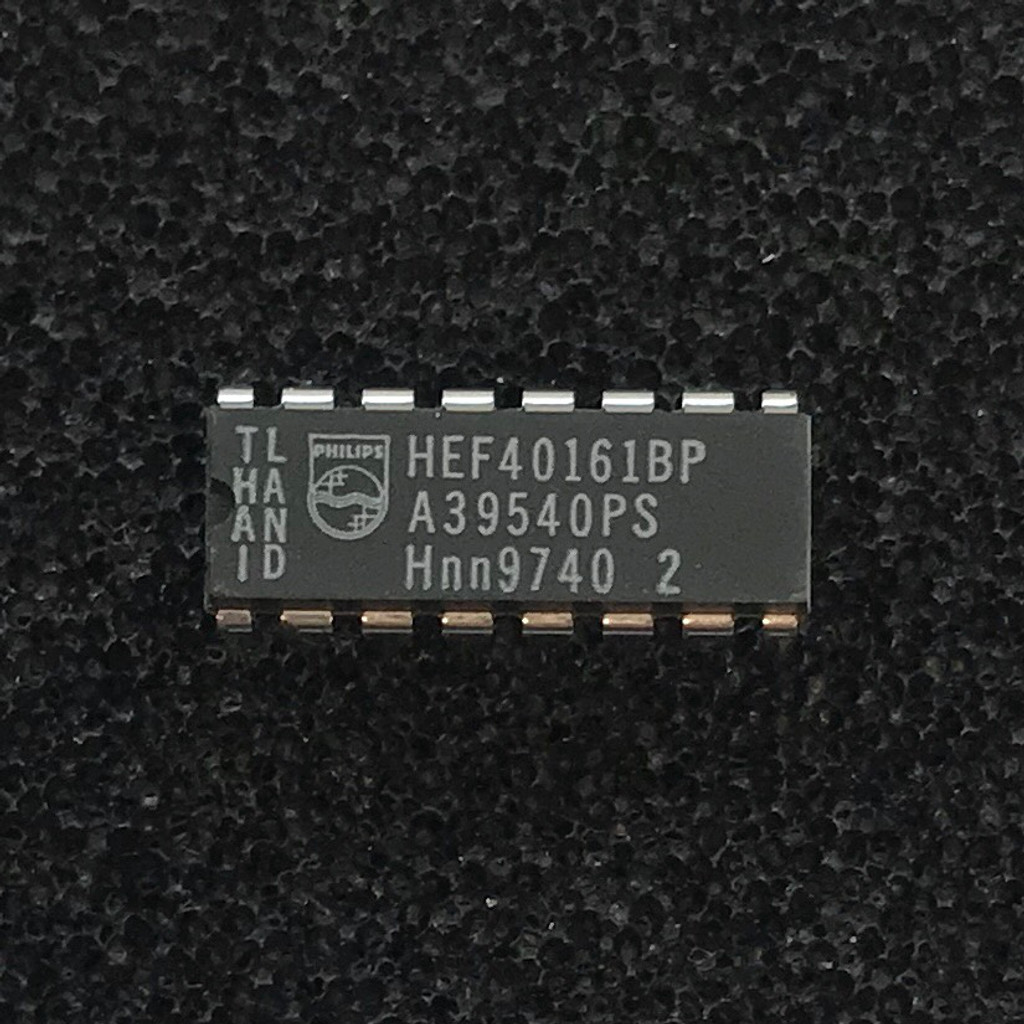

(PKG of 10) HEF40161BP 4-Bit Binary Counter CD40161, PDIP-16, Philips

Package of 10!

New old stock (NOS), unused, genuine part: Philips HEF40161BP 4-bit Binary Counter with Asynchronous Reset, PDIP-16 package.

Manufacturer: Philips

Manufacturer Part Number: HEF40161BP

Product Category: Counter ICs, Binary

Logic Family: CD4000 (CD40161)

Number of bits: 4 bit

Counting Sequence: Up

Package / Case: PDIP-16

RoHS: NO

Packaging: Anti-Static

Description

The HEF40161B is a fully synchronous edge-triggered 4-bit binary counter with a clock input (CP), an overriding asynchronous master reset (MR), four parallel data inputs (P0 to P3), three synchronous mode control inputs (parallel enable (PE), count enable parallel (CEP) and count enable trickle (CET)), buffered outputs from all four bit positions (O0 to O3) and a terminal count output (TC).

Operation is fully synchronous (except for the MR input) and occurs on the LOW to HIGH transition of CP. When PE is LOW, the next LOW to HIGH transition of CP loads data into the counter from P0 to P3 regardless of the levels of CEP and CET inputs.

When PE is HIGH, the next LOW to HIGH transition of CP advances the counter to its next state only if both CEP and CET are HIGH; otherwise, no change occurs in the state of the counter. TC is HIGH when the state of the counter is 15 (O1 to O3 = HIGH) and when CET is HIGH. A LOW on MR sets all outputs (O0 to O3 and TC) LOW, independent of the state of all other inputs. Multistage synchronous counting is possible without additional components by using a carry look-ahead counting technique; in this case, TC is used to enable successive cascaded stages. CEP, CET and PE must be stable only during the set-up time before the LOW to HIGH transition of CP.

Description

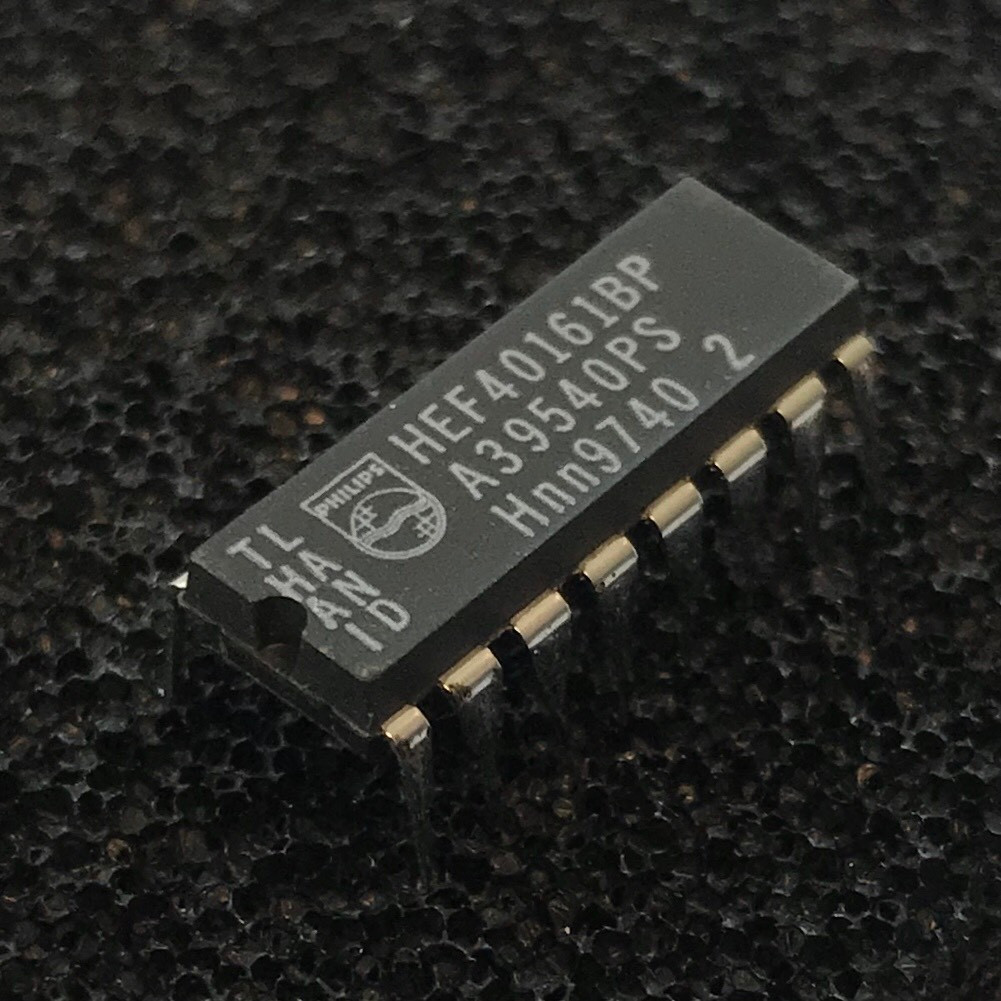

Package of 10!

New old stock (NOS), unused, genuine part: Philips HEF40161BP 4-bit Binary Counter with Asynchronous Reset, PDIP-16 package.

Manufacturer: Philips

Manufacturer Part Number: HEF40161BP

Product Category: Counter ICs, Binary

Logic Family: CD4000 (CD40161)

Number of bits: 4 bit

Counting Sequence: Up

Package / Case: PDIP-16

RoHS: NO

Packaging: Anti-Static

Description

The HEF40161B is a fully synchronous edge-triggered 4-bit binary counter with a clock input (CP), an overriding asynchronous master reset (MR), four parallel data inputs (P0 to P3), three synchronous mode control inputs (parallel enable (PE), count enable parallel (CEP) and count enable trickle (CET)), buffered outputs from all four bit positions (O0 to O3) and a terminal count output (TC).

Operation is fully synchronous (except for the MR input) and occurs on the LOW to HIGH transition of CP. When PE is LOW, the next LOW to HIGH transition of CP loads data into the counter from P0 to P3 regardless of the levels of CEP and CET inputs.

When PE is HIGH, the next LOW to HIGH transition of CP advances the counter to its next state only if both CEP and CET are HIGH; otherwise, no change occurs in the state of the counter. TC is HIGH when the state of the counter is 15 (O1 to O3 = HIGH) and when CET is HIGH. A LOW on MR sets all outputs (O0 to O3 and TC) LOW, independent of the state of all other inputs. Multistage synchronous counting is possible without additional components by using a carry look-ahead counting technique; in this case, TC is used to enable successive cascaded stages. CEP, CET and PE must be stable only during the set-up time before the LOW to HIGH transition of CP.

Reviews (0)

Be the first to write a review